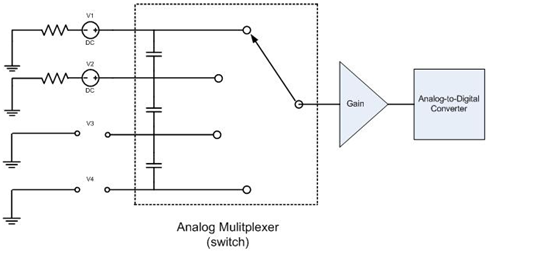

低成本數據采集設備(DAQ)通常使用單個模數轉換器(ADC)對多個通道進行采樣。為了采樣多個通道,DAQ使用固態模擬多路復用器IC。一個典型單元的示例可能具有16個電壓輸入通道和一個ADC,要求每個通道與ADC共享時間。當今一些更好的設備將ADC專用于每個通道,但這要付出額外的費用。將來,隨著芯片價格的持續下降,每個通道的ADC將會普及。但是,在此之前,DAQ用戶應該了解信號源阻抗如何影響信號測量。

所有多通道單ADC多路復用DAQ,例如IOtech的3000系列產品線,都具有由雜散電容引起的一定程度的電荷耦合效應(串擾)。電荷耦合影響信號的程度稱為通道間串擾,通常以負dB表示。理想情況下,對于16位轉換器,串擾規范應為-96dB,但實際上并非如此。要確定此規范將如何影響讀數,請使用一個具有-75dB串擾的簡單兩通道系統,其中通道1的測量值為6.0 Vdc,而通道2的測量值為0.0 Vdc。-75dB規范告訴我們,某些6.0 Vdc會進入0.0 Vdc,這可以通過以下公式確定:

串擾= 20 Log(X / 6.0Vdc)

X = inv Log(-75dB / 20)* 6.0 Vdc

X = 1.06毫伏

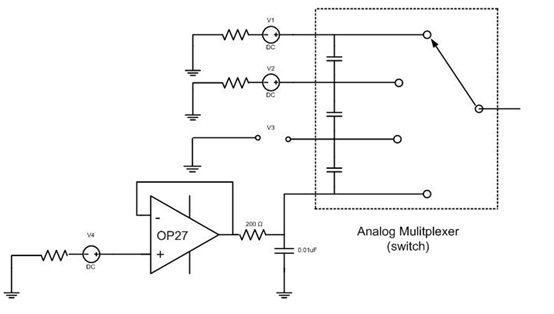

上面是描繪通道之間雜散電容的典型系統。它還將輸入信號顯示為理想的電壓源和相關的電阻。在工作期間,多路復用器從通道1切換到通道2,并再次切換到通道1(對于我們的示例),正是這種切換動作導致雜散電容兩端出現電壓尖峰。由于電壓尖峰是交流信號,因此電容的作用類似于瞬時短路,將一些電壓施加到下一個通道。該電壓沒有太多能量,并且會通過施加信號的源阻抗(電阻)迅速(呈指數方式)耗散。希望到現在為止,可以很容易地想象出當源阻抗很大時會發生什么。

為了最大程度地減少串擾,系統需要優化建立時間和源阻抗。如果DAQ單元的電路可以在通道之間以高速度切換回去,那么具有低阻抗的信號就非常重要。另一方面,如果開關時間在幾秒的范圍內,則源阻抗就不太重要。理想的源阻抗應為零,但實際上100歐姆以下是好的。對于許多高速設備(例如3000系列),增加的建立時間不是可調參數,因為其時鐘電路由固定的1MHz時鐘驅動。因此,不可能通過增加建立時間來克服高源阻抗問題。因此,應將源阻抗最小化以保持精度。

緩沖電路通常用于將高阻抗轉換為低阻抗,如下所示。重要的是要注意,因為開關時間很快,所以應該使用像OP27這樣的快速運算放大器。否則,多路復用器的快速脈沖會干擾較慢的運算放大器輸出級,從而抵消了緩沖器的任何積極影響。

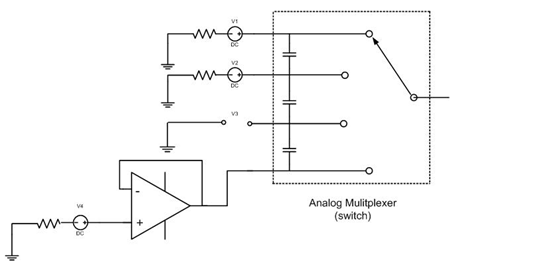

根據信號吞吐量的不同,較慢的運算放大器如INA128可以與低通電路一起使用,如下所示: