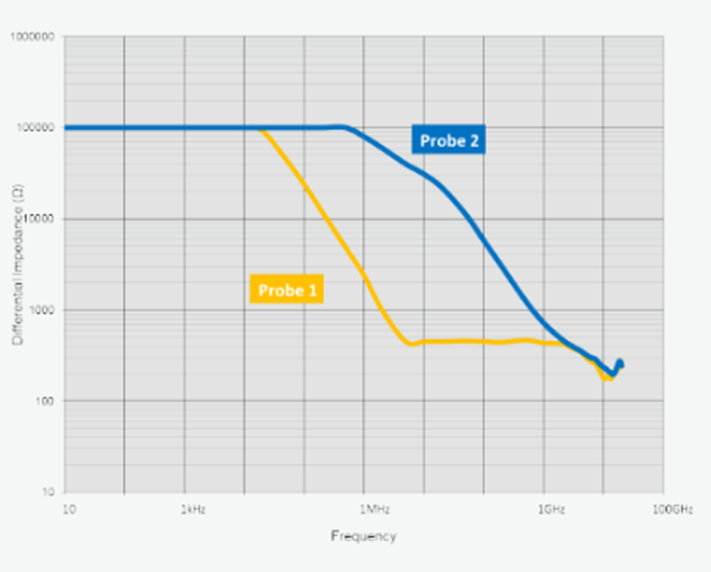

探頭前端的高頻設計折衷會影響其輸入阻抗。讓我們考慮使用具有不同設計的兩個高性能探頭對設備的實際影響。兩個探頭的輸入阻抗如圖 1 所示。很明顯,探頭設計人員在他們的探頭設計中做出了不同的選擇。一個選擇了較高的電容輸入,其中阻抗在相對較低的頻率下降至 Z min (探頭 1)。而另一個創建了一個較低的電容設計,在下降到 Z min之前保持其對高頻的阻抗(探頭 2)。

圖 1. 兩種探頭設計的輸入阻抗曲線。

過去,設計像探頭 2 這樣的高阻抗輸入通常意味著探頭的帶寬會受到限制。而像探頭 1 這樣的設計以較低的輸入阻抗為代價實現了高帶寬。這不再適用,因為現在有一個具有探頭 2 輸入阻抗的 20 GHz 帶寬探頭。有關詳細信息,請參閱邊欄:“P7700 Chip-on-theTip 技術”。

探測示例 1:高速串行

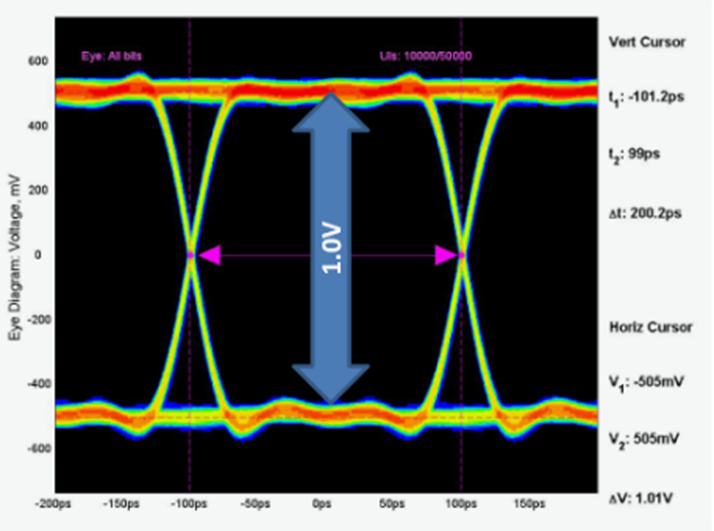

讓我們看看這兩個探頭的不同輸入阻抗對實際信號的影響。從 8 Gb/s 高速串行 (HSS) 鏈路的眼圖開始并連接每個探頭,我們將研究由于探頭負載而導致的信號變化。該 HSS 信號的標稱幅度為 ±500mV。圖 2 表示處于空載狀態的信號。此圖表示在完成任何探測之前發射器輸出的信號。

圖 2. 高速串行總線空載(參考)。

當探針連接到該電路時,一部分信號電流被探針移除。圖 8 顯示了具有高電容輸入的探頭 1 的結果。由于探頭 1 在低頻和高頻下看起來像一個低阻抗,高速串行信號上的負載很明顯,但在信號的寬頻率分量范圍內相似。這種負載意味著接收器看到的信號已從 ±500mV 降低到 ±450mV,或降低 10%。

圖 3. 連接了探頭的高速串行總線。

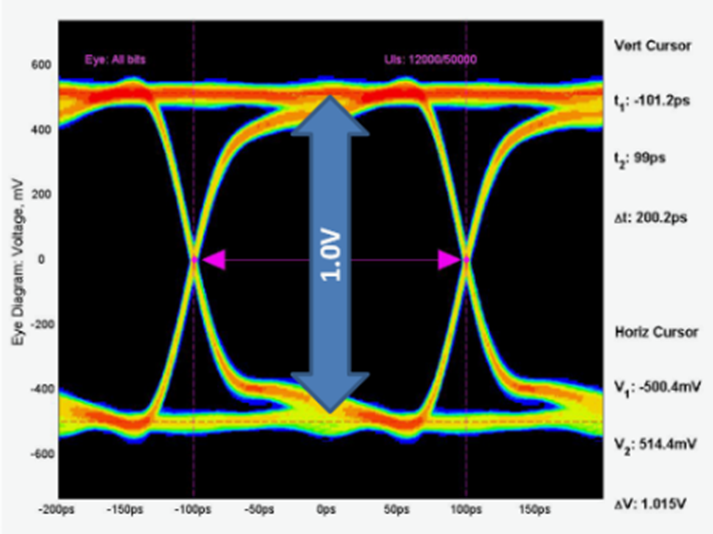

圖 4 顯示了探頭 2 在低頻和中頻具有高阻抗,在低頻到中頻對電路的負載非常小。與參考眼睛相比,眼睛的頂線和基線的峰值幅度非常相似。當信號以非常快的上升沿或下降沿改變電平時,眼圖的顯著變化發生在較高的頻率上。

圖 4. 連接了探頭 2 的高速串行信號。

在高頻下加載此探頭會創建一個具有不對稱外觀的眼圖,并且接收器看到的信號的上升和下降時間較慢。雖然這兩個探頭的阻抗以不同的方式加載 HSS 信號,但串行鏈路可能會繼續可靠地運行,因為眼圖仍然大開。